RTL Design/Verilog RTL 설계

Verilog RTL 설계 (6월 13일 - 4)

유로 청년

2024. 6. 15. 16:02

1. 1bit Comparator

- 1bit 비교기는 1bit 데이터 2개를 입력받아 두 값을 비교하여 1) A > B인지 2) A == B인지 3) A < B인지를 결과값으로 출력하는 논리 회로를 의미한다.

- 1bit 비교기의 Truth table 과 논리 회로는 다음과 같다.

2. 1bit Comparator ( Behavior modeling )

< Source >

module comparator_1bit_behavior_modeling(

input a, b,

output reg equal, greater, less );

always @(*) begin

case({a, b})

2'b00 : begin equal = 1; greater = 0; less = 0; end

2'b01 : begin equal = 0; greater = 0; less = 1; end

2'b10 : begin equal = 0; greater = 1; less = 0; end

2'b11 : begin equal = 1; greater = 0; less = 0; end

endcase

end

endmodule

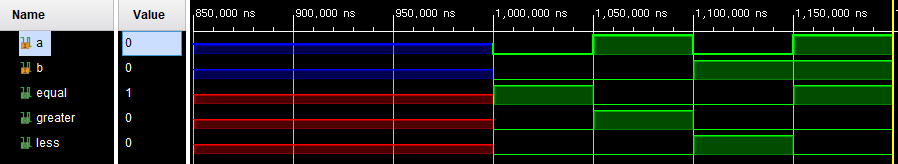

< Simulation >

3. 1bit Comparator ( Structural modeling )

< Source >

module comparator_1bit_structural_modeling(

input a, b,

output equal, greater, less );

// equal output port

xnor(equal, a, b);

wire not_a, not_b;

not(not_a, a);

not(not_b, b);

// greater output port

and(greater, a, not_b);

// less output port

and(less, not_a, b);

endmodule

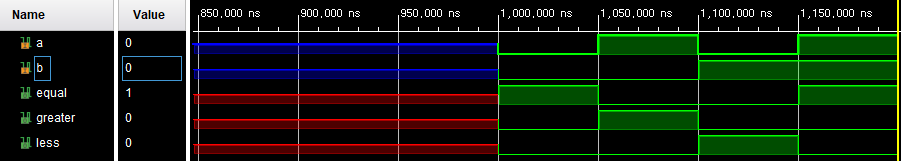

< Simulation >

4. 1bit Comparator ( Dataflow modeling )

< Source >

module comparator_1bit_dataflow_modeling(

input a, b,

output equal, greater, less );

assign equal = (a == b)? 1 : 0;

assign greater = (a > b)? 1: 0;

assign less = (a < b)? 1: 0;

endmodule

< Simulation >

5. 4bit Comparator ( Dataflow modeling )

< Source >

module comparator_4bit_dataflow_modeling(

input [3:0] a, b,

output equal, greater, less);

assign equal = (a == b)? 1 : 0;

assign greater = (a > b)? 1 : 0;

assign less = (a < b)? 1 : 0;

endmodule

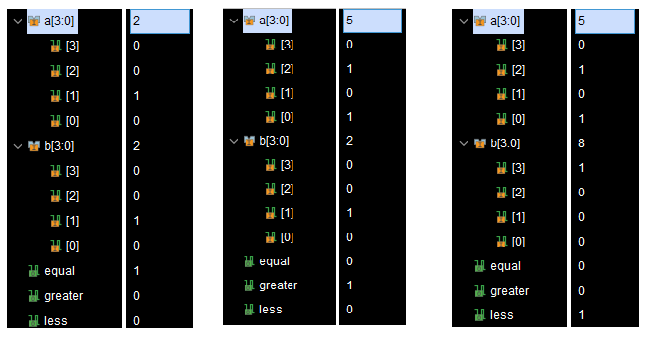

< Simulation >

- Q) 왜 Structural modeling, Behavior modeling 으로 설계를 하지 않았는가?

A) 입력 값인 4bit a, b으로 만들 수 있는 경우의 수는 2^8 = 256개 이기 때문에 이에 대한 출력을 설계하는 것은 힘들기 때문에 Dataflow modeling으로 구현 했다.

6. 32bit Comparator ( Dataflow modeling )

< Source >

module comparator_32bit_dataflow_modeling(

input [31:0] a, b,

output equal, greater, less );

assign equal = (a == b)? 1 : 0;

assign greater = (a > b)? 1 : 0;

assign less = (a < b)? 1 : 0;

endmodule

< Simulation >

- 2^32개의 입력으로 모두 설정하기 힘들어서....

7. Dataflow modeling에서 사용되는 연산자들은 32bit 단위로 처리한다.

- 이전에 full adder, half adder, parallel adder에서 사용했던 + (덧셈 회로), - (뺄셈 회로)는 32bit 단위로 처리하고, 연산의 결과도 32bit로 나타난다고 확인했다.

- 이번 Comparator를 Dataflow modeling 에서 사용했던 비교 연산자들 또한 32bit 단위로 비교 연산 및 처리한다.

- 하지만, 64bit system에서 연산한다면 연산하는 단위가 64bit로 확장된다.