RTL Design/Verilog 연습

Half adder

유로 청년

2024. 6. 29. 21:10

1. Half adder

1.1. Behavioral Modeling (by using case)

<Source>

// Behavioral modeling of Half adder

module Half_adder_Behavioral_Modeling(

input a, b,

output reg carry, sum);

always @(a, b) begin

case({a, b})

2'b00 : begin carry = 0; sum = 0;end

2'b01 : begin carry = 0; sum = 1;end

2'b10 : begin carry = 0; sum = 1;end

2'b11 : begin carry = 1; sum = 0;end

endcase

end

endmodule

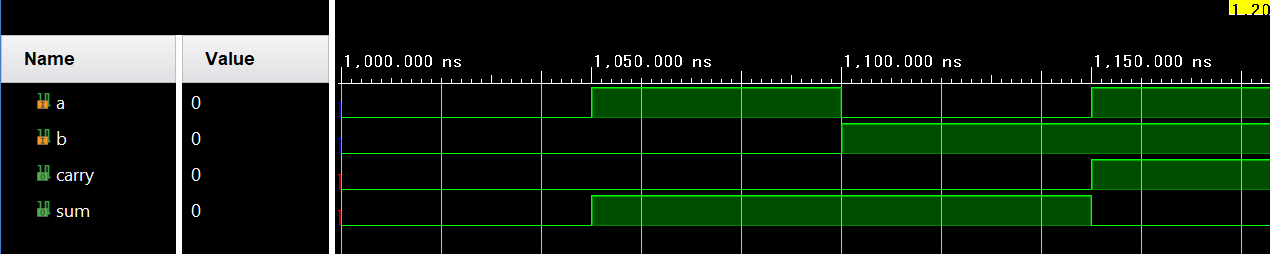

<Simulation>

<RTL Analysis>

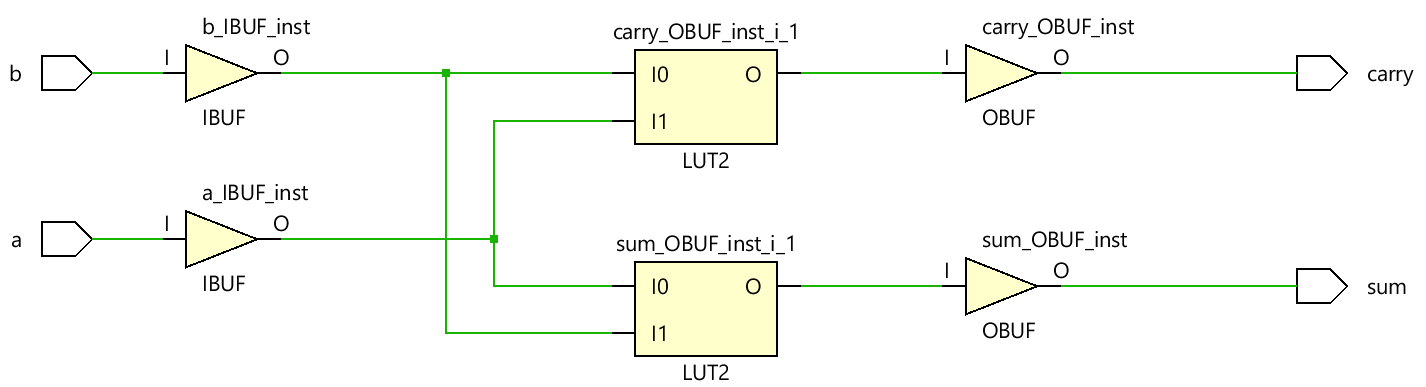

<Synthesis>

1.2. Structural Modeling

<Source>

// Behavioral modeling of and gate.

module and_gate (

input a, b,

output reg out);

always @(a, b) begin

case({a, b})

2'b00 : out = 0;

2'b01 : out = 0;

2'b10 : out = 0;

2'b11 : out = 1;

endcase

end

endmodule

// Behavioral modeling of xor gate.

module xor_gate (

input a, b,

output reg out);

always @(a, b) begin

case({a, b})

2'b00 : out = 0;

2'b01 : out = 1;

2'b10 : out = 1;

2'b11 : out = 0;

endcase

end

endmodule

// Structural modeling of half adder

module Half_adder_Structural_Modeling(

input a, b,

output sum, carry);

and_gate and0 (a, b, carry);

xor_gate xor0 (a, b, sum);

endmodule

<Simulation>

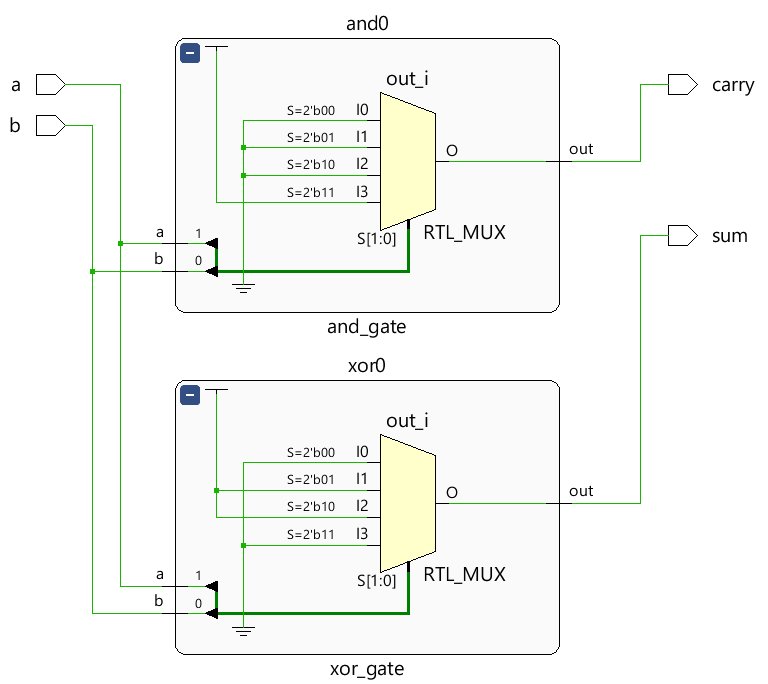

<RTL Analysis>

<Synthesis>

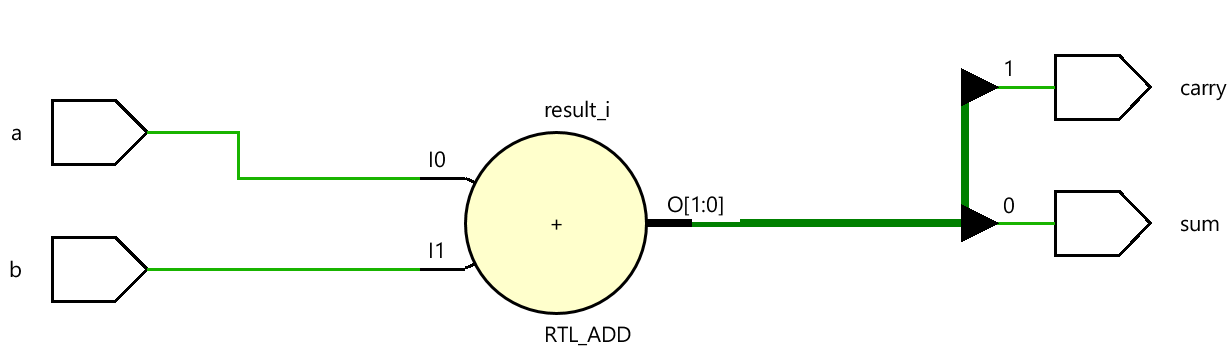

1.3. Dataflow Modeling

<Source>

// Dataflow modeling of Half adder

module Half_adder_Dataflow_modeling(

input a, b,

output sum, carry);

wire [1:0] result = a + b;

assign sum = result[0];

assign carry = result[1];

endmodule

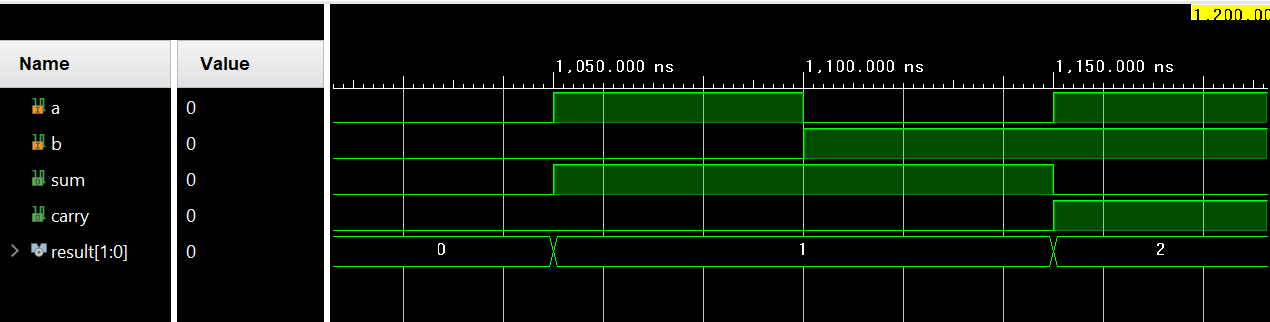

<Simulation>

<RTL Analysis>

<Synthesis>