논리 회로/디지털 논리 회로

4 bit parallel adder (4비트 병렬 가산기)

유로 청년

2024. 7. 2. 08:45

1. 4비트 병렬 가산기

- 병렬 가산기는 Full adder를 병렬로 연결하여 2bit 이상의 2진수를 덧셈 연산할 수 있는 가산기이다.

- 각각의 Full adder들은 각 비트에서 독립적으로 덧셈연산을 수행하며, LSB을 제외한 나머지 비트에 해당하는 Full adder들은 이전 비트에서 발생한 Carry 값을 받아 연산한다.

- 이전 비트로 부터 Carry값을 받아야 연산 할 수 있기 때문에 PDT (Propagation Delay Time)이 발생한다.

2. 4비트 병렬 가산기의 구현 (PSpice)

< Digital Circuit >

< Simulation >

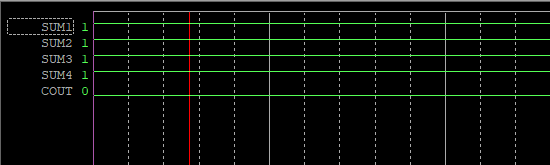

- 입력 A : 0011, B : 1010

- 출력 Cout = 0, Sum = 1101

< Simulation >

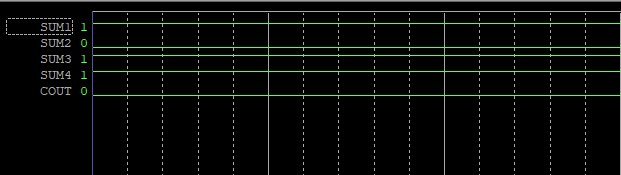

- 입력 A : 1010, B : 0101

- 출력 Cout = 0, Sum = 1111