RTL Design/Verilog 연습

JK Flip Flop

유로 청년

2024. 7. 11. 11:35

1. Behavioral modeling of JK Flip Flop (Positive edge)

< Source code >

// Behavioral modeling of JK Flip Flop

module Behavioral_modeling_of_JK_Flip_Flop_Positive(

input j, k,

input clk, enable, reset,

output reg q );

always @(posedge clk or posedge reset) begin

if(reset) q = 0;

else if(enable) begin

if(j == 0 && k == 0) q = q;

else if(j == 1 && k == 0) q = 1;

else if(j == 0 && k == 1) q = 0;

else q = ~q;

end

else q = q;

end

endmodule

< Simulation >

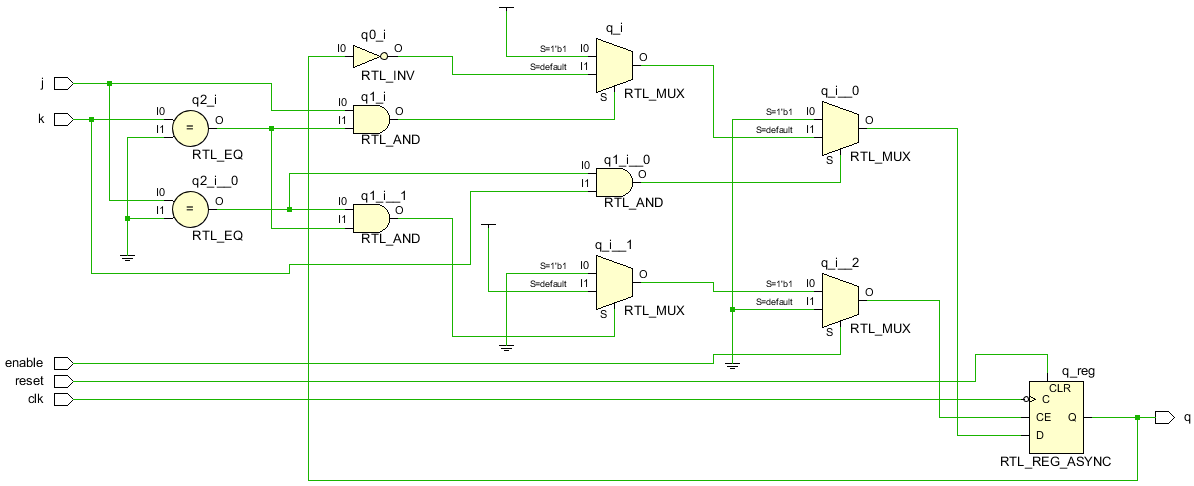

< RTL analysis >

< Synthesis >

2. Behavioral modeling of JK Flip Flop (Negative edge)

< Source code >

// Behavioral modeling of JK Flip Flop

module Behavioral_Modeling_of_JK_Flip_Flop_Negative(

input j, k,

input clk, enable, reset,

output reg q );

always @(negedge clk or posedge reset) begin

if(reset) q = 0;

else if(enable) begin

if(j == 0 && k ==0) q = q;

else if(j == 0 && k ==1) q = 0;

else if(j == 1 && k ==0) q = 1;

else q = ~q;

end

else q = q;

end

endmodule

< Simulation >

< RTL analysis >

< Synthesis >