RTL Design/Verilog 연습

비동기식 카운터 (Asynchronous counter)

유로 청년

2024. 7. 11. 21:44

1. Asynchronous MOD 16 up counter, T Flip-Flop

< Source code >

// Behavioral modeling of T Flip Flop

module t_flip_flop (

input t,

input clk, enable, reset,

output reg q );

always @(negedge clk or posedge reset) begin

if(reset) q = 0;

else if(enable) q = (t)? ~q : q;

else q = q;

end

endmodule

// Asynchronous up counter MOD 10

module Asynchronous_Up_Counter_MOD_10_T_Flip_Flop(

input clk, enable, reset,

output [3:0] result );

t_flip_flop t_flip_flop_0 (1, clk, enable, reset, result[0]);

t_flip_flop t_flip_flop_1 (1, result[0], enable, reset, result[1]);

t_flip_flop t_flip_flop_2 (1, result[1], enable, reset, result[2]);

t_flip_flop t_flip_flop_3 (1, result[2], enable, reset, result[3]);

endmodule

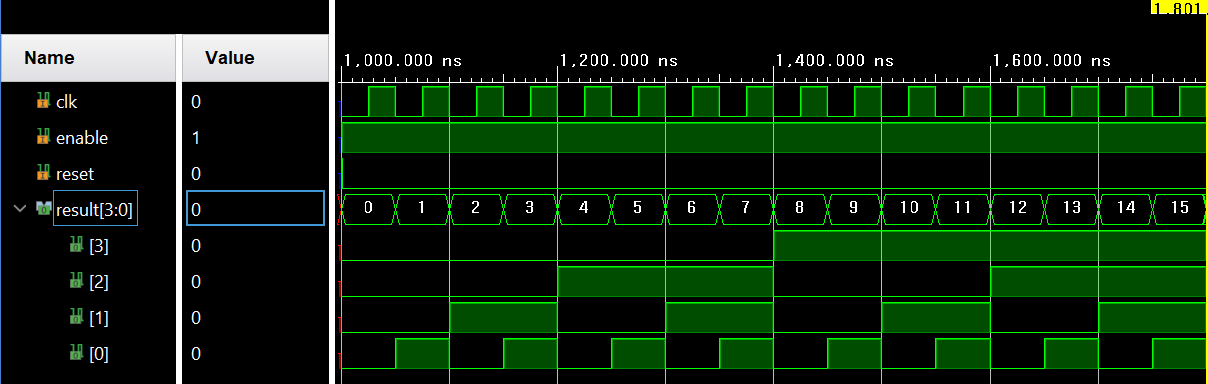

< Simulation >

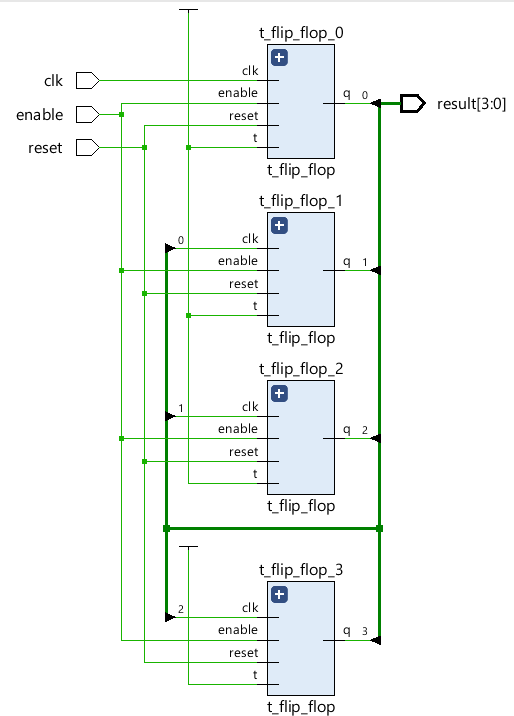

< RTL analysis >

< Synthnesis >

2. Asynchronous MOD 16 down counter, T Flip-Flop

< Source code >

// Behavioral modeling of T Flip Flop

module t_flip_flop (

input t,

input clk, enable, reset,

output reg q );

always @(posedge clk or posedge reset) begin

if(reset) q = 0;

else if(enable) q = (t)? ~q : q;

else q = q;

end

endmodule

// Asynchronous MOD 16 Down counter

module Asynchronous_Down_Counter_MOD_16__T_Flip_Flop(

input clk, enable, reset,

output [3:0] result );

t_flip_flop t_flip_flop_0 (1, clk, enable, reset, result[0]);

t_flip_flop t_flip_flop_1 (1, result[0], enable, reset, result[1]);

t_flip_flop t_flip_flop_2 (1, result[1], enable, reset, result[2]);

t_flip_flop t_flip_flop_3 (1, result[2], enable, reset, result[3]);

endmodule

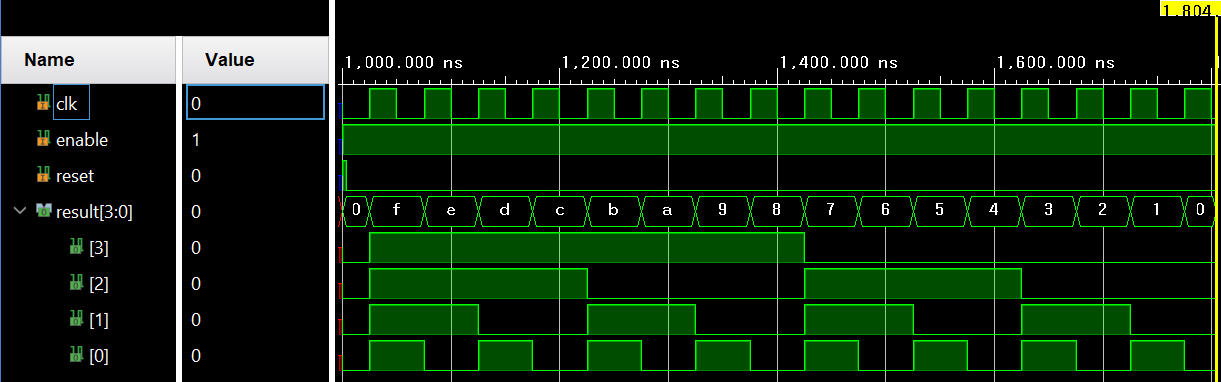

< Simulation >

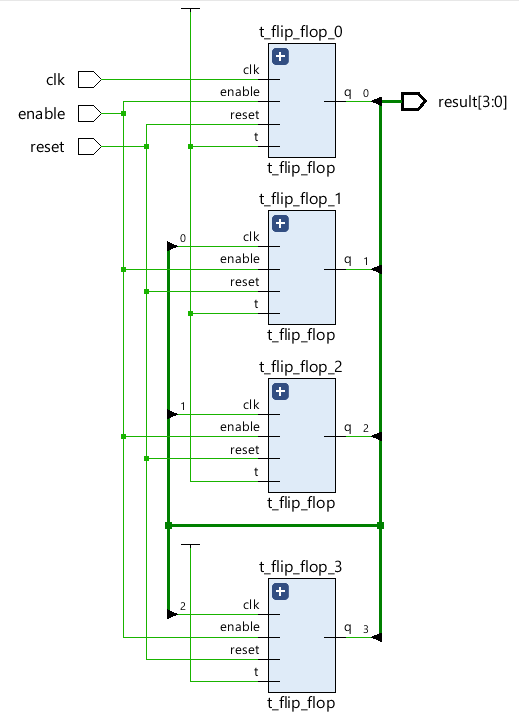

< RTL analysis >

< Synthnesis >