RTL Design/Verilog RTL 설계

Verilog RTL 설계(7월 12일 - 5, 동기식 업/다운 카운터)

유로 청년

2024. 7. 14. 20:19

1. Synchronous Up Down Counter (Negative edge trigger)

- Up counter로 동작하며, Down Counter로서 동작할 수 있다.

< Source >

// Syncrhronous Up Down Counter implemented with D Flip Flop

module Synchronous_Up_Down_Counter_Negative(

input up_down,

input clk, enable, reset_p,

output reg [3:0] count );

// 0 : Up Counting, 1 : Down Counting

always @(negedge clk or posedge reset_p) begin

if(reset_p) count = 0;

else if(enable) begin

if(up_down) count = count - 1;

else count = count + 1;

end

else count = count;

end

endmodule

< Simulation >

- up_down 변수가 0인 경우 (= Up Counter로 동작하는 경우)

- up_down 변수가 1인 경우 (= Down Counter로 동작하는 경우)

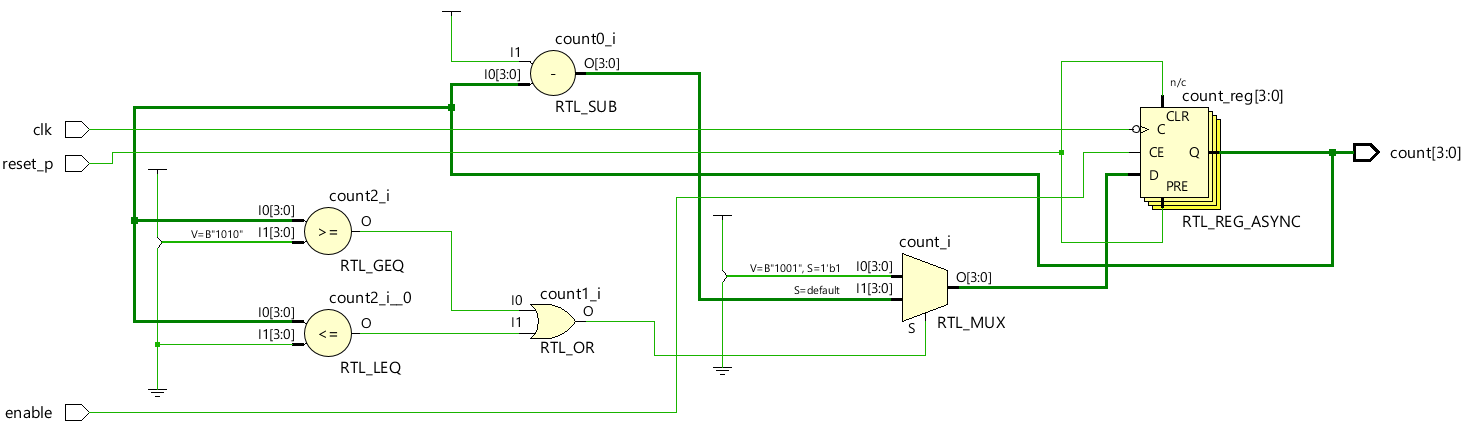

< RTL Analysis >

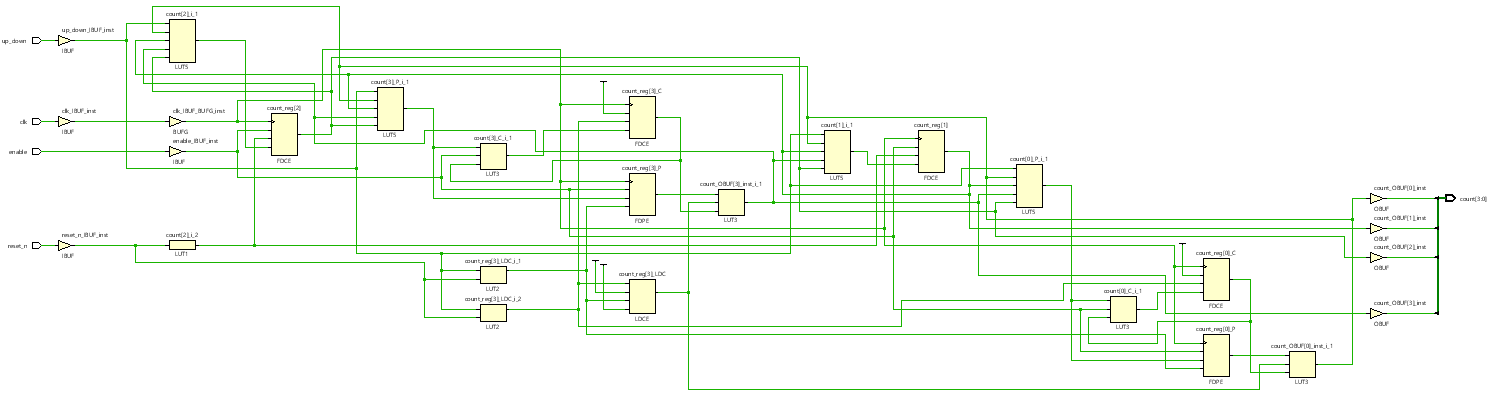

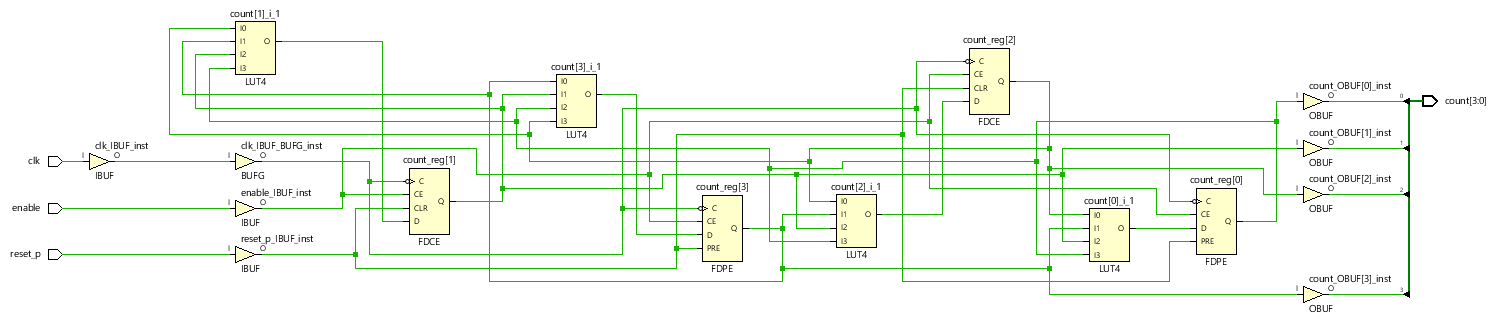

< Synthesis >

2. Synchronous BCD Up Down Counter (Positive edge trigger)

< Source >

// Synchronous BCD Up Down Counter implemented with D Flip Flop (Positive)

module Synchronous_BCD_Up_Down_Counter_Positive(

input up_down,

input clk, enable, reset_n,

output reg [3:0] count );

// Up Counter : 1, Down Counter : 0

always @(posedge clk or negedge reset_n) begin

if(!reset_n) begin

if(up_down) count = 0;

else count = 9;

end

else if(enable) begin

if(up_down) begin

if(count >= 9) count = 0;

else count = count + 1;

end

else begin

if(count >= 10 | count <=0) count = 9;

count = count - 1;

end

end

else count = count;

end

endmodule

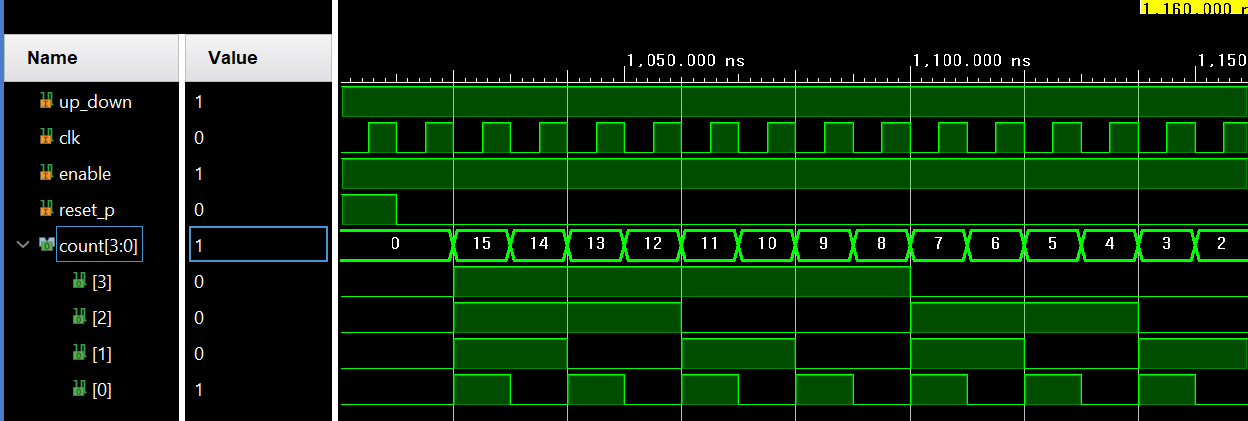

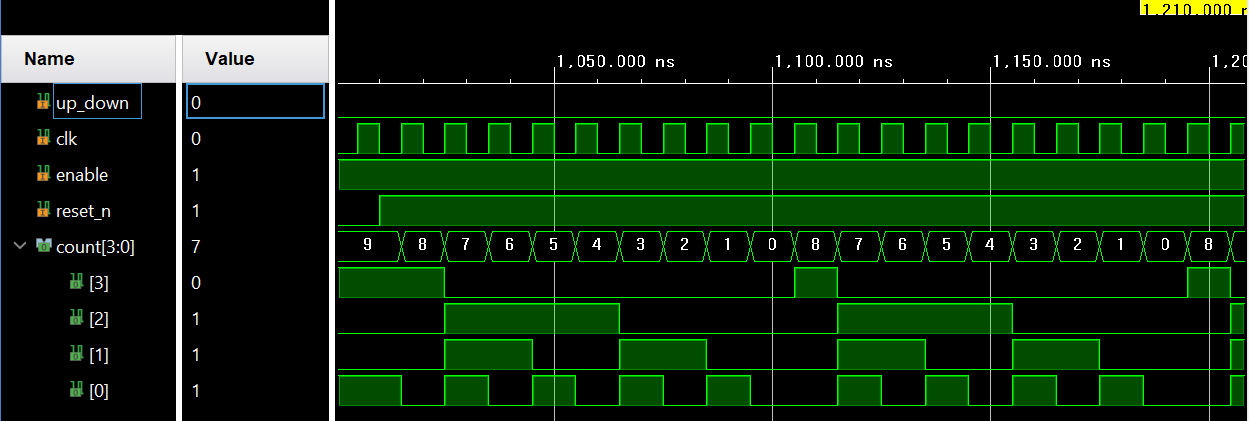

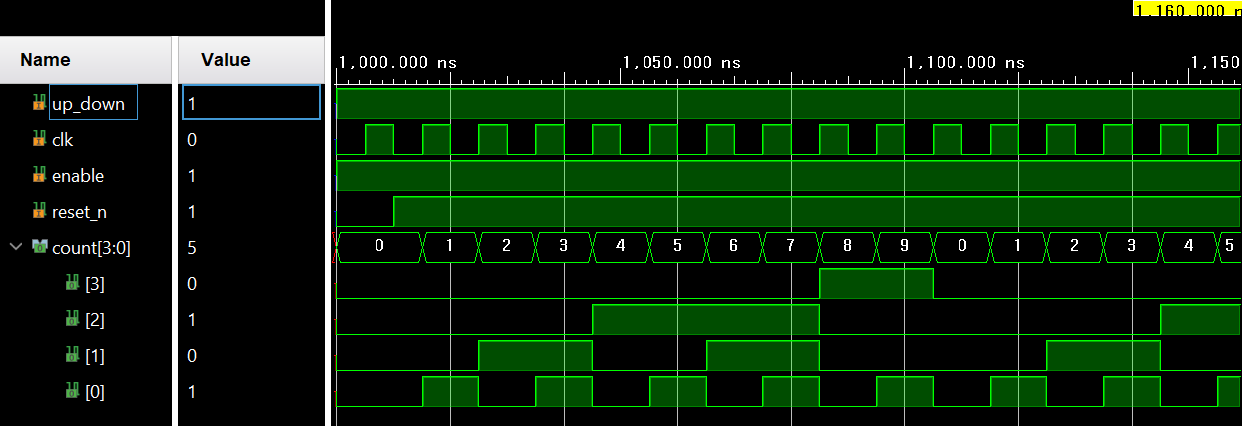

< Simulation >

- up_down 변수가 0인 경우 (= Down Counter로 동작하는 경우)

- up_down 변수가 1인 경우 (= Up Counter로 동작하는 경우)

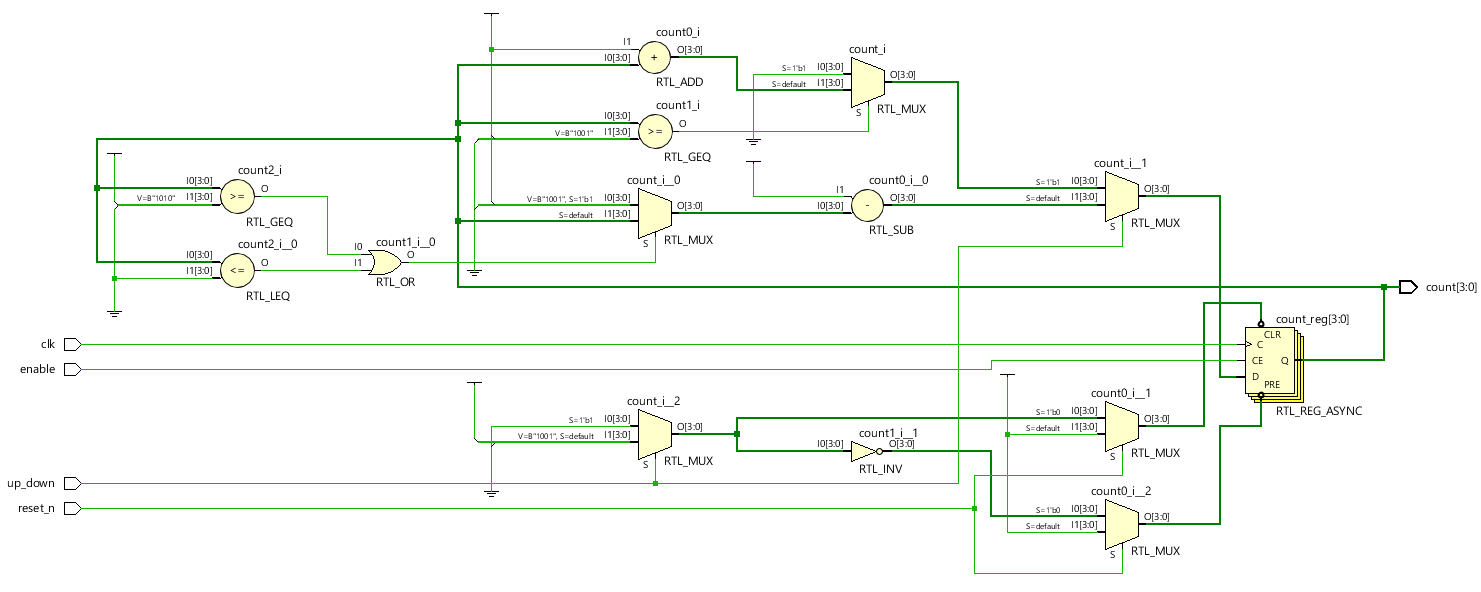

< RTL Analysis >

< Synthesis >