RTL Design/Verilog RTL 설계

Verilog RTL 설계(7월 16일 - 5, 16진수 값을 FND로 출력)

유로 청년

2024. 7. 18. 18:42

1. 4bit 데이터 변수에 담겨 있는 16진수 값을 FND에 출력하기

- 4bit 크기를 갖는 변수에 16진수 값을 저장한 뒤, 이를 FND로 출력하도록 설계한다.

- 동작은 다음과 같이 동작한다.

- Common anode는 Switch 0번 ~ 3번를 통해 Control 한다.

- Hex value는 Switch 12번 ~ 15번을 통해 표현 하게 된다.

- 12번 ~ 15번까지의 Switch로 표현된 16진 값을 4개의 FND에 동시 출력되도록 한다.

1.1. Hex value를 모듈의 입력 값으로 전달하게 되면 이를 출력하기 위한 8개의 다이오드의 출력 정보를 출력한다.

- Hex value를 모듈의 입력 값으로 전달해야 하기 때문에 입력값은 4bit 크기를 갖는다.

- 8개의 다이오드의 출력 정보를 출력하기 위해서는 8bit 크기를 가져야 한다.

- 4bit 데이터를 입력 받아 8bit 데이터로 출력하는 과정이 마치 Decoder 수행 작업과 유사하기 때문에 해당 코드를 Synthesis 될 경우 Decoder가 생성 될 것이라고 유추 할 수 있다.

< Source code >

module decoder_7_Segment (

input [3:0] hex_value,

output reg [7:0] seg_7 );

always @(hex_value) begin

case(hex_value)

0 : seg_7 = 8'b0000_0011; // 0

1 : seg_7 = 8'b1001_1111; // 1

2 : seg_7 = 8'b0010_0101; // 2

3 : seg_7 = 8'b0000_1101; // 3

4 : seg_7 = 8'b1001_1001; // 4

5 : seg_7 = 8'b0100_1001; // 5

6 : seg_7 = 8'b0100_0001; // 6

7 : seg_7 = 8'b0001_1111; // 7

8 : seg_7 = 8'b0000_0001; // 8

9 : seg_7 = 8'b0000_1001; // 9

10 : seg_7 = 8'b0000_0101; // A

11 : seg_7 = 8'b1100_0001; // b

12 : seg_7 = 8'b0110_0011; // C

13 : seg_7 = 8'b1000_0101; // d

14 : seg_7 = 8'b0110_0001; // E

15 : seg_7 = 8'b0111_0001; // F

endcase

end

endmodule

1.2. FND 데이터를 입력 받은 뒤, 해당 모듈을 출력한다.

- decoder_7_Segment 모듈로 부터 얻은 FND 출력 데이터를 seg_7 출력 단자에 출력시킨다.

< Source >

module FND_Print_Hex_Value_By_Using_Switch(

input clk, reset_p,

input [15:0] switch,

output [3:0] com,

output [7:0] seg_7);

assign com = switch[3:0];

decoder_7_Segment decoder_7_seg (switch[15:12], seg_7);

endmodule

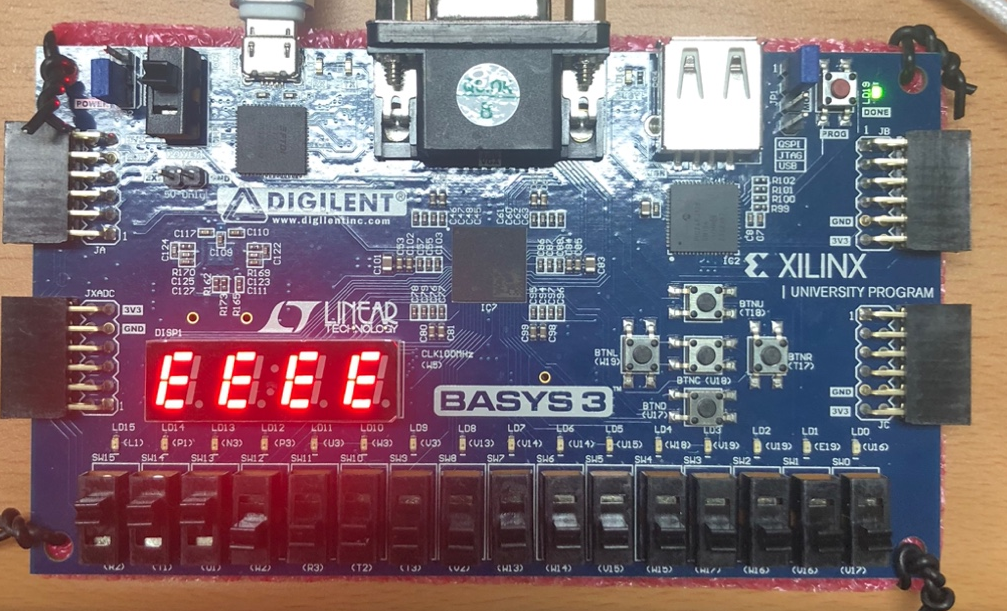

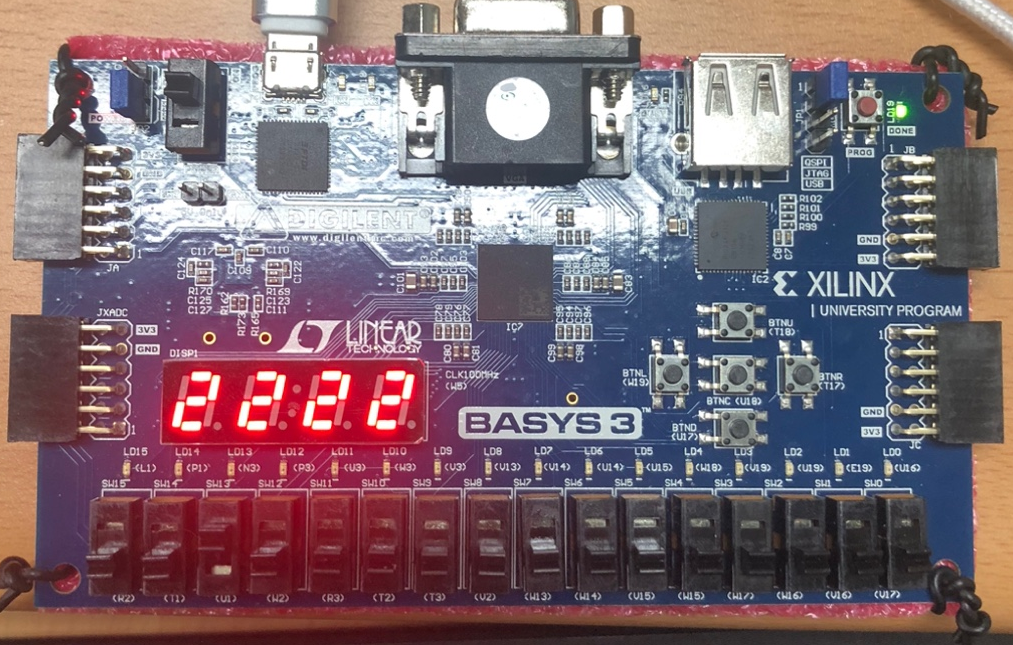

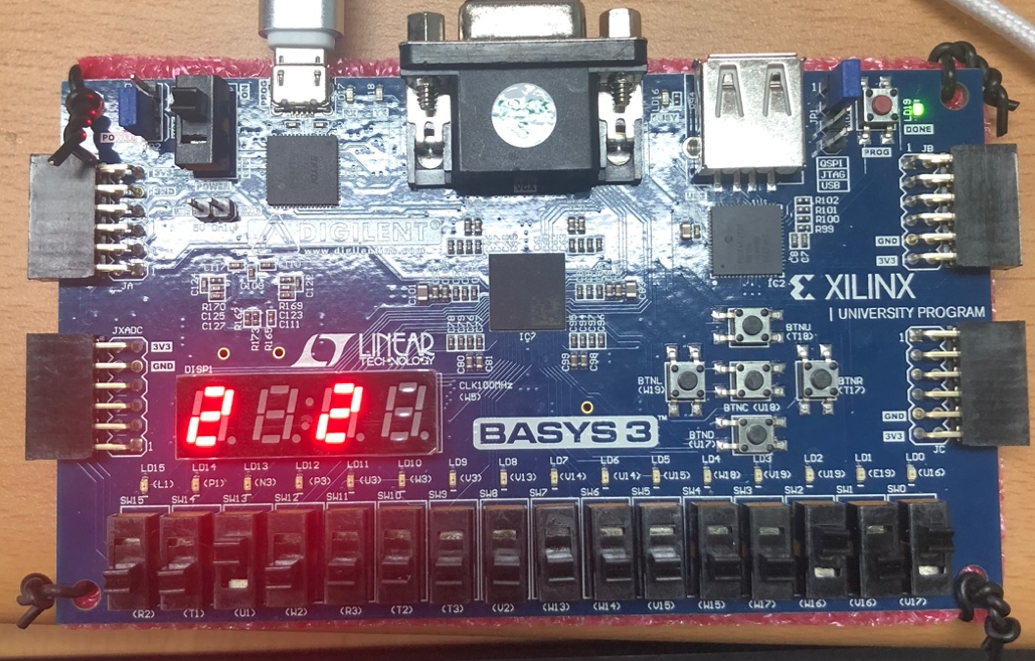

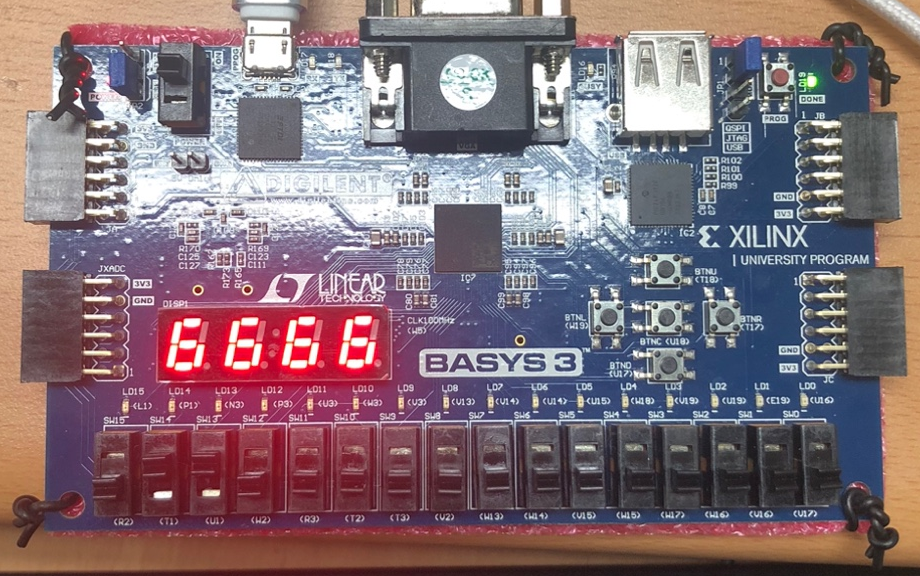

1.3. 구현

- com = 4'b0000, seg_7 = 8'b0010_0101

- com = 4'b0101, seg_7 = 8'b0010_0101

- com = 4'b0000, seg_7 = 8'b0100_0001

- com = 4'b0000, seg_7 = 8'b0110_0001