Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| 30 |

Tags

- prescaling

- LED

- BASYS3

- java

- ring counter

- stop watch

- gpio

- structural modeling

- soc 설계

- ATMEGA128A

- uart 통신

- Recursion

- dataflow modeling

- vivado

- hc-sr04

- KEYPAD

- Pspice

- Edge Detector

- i2c 통신

- atmega 128a

- DHT11

- pwm

- Algorithm

- D Flip Flop

- verilog

- test bench

- Linked List

- FND

- behavioral modeling

- half adder

Archives

- Today

- Total

거북이처럼 천천히

Verilog RTL 설계 (6월 24일 - 2) 본문

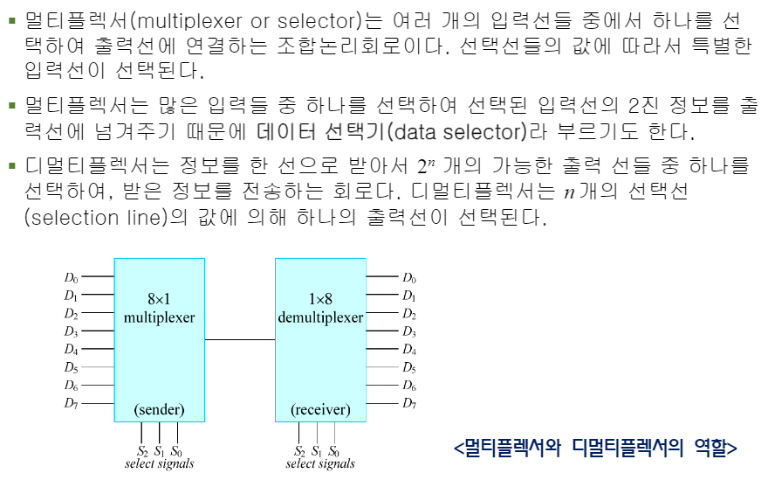

1. 멀티플렉서 (MUX, Multiplxer or Selector)

- MUX는 2^n 개 입력 단자를 통해 동시에 여러 입력값이 들어오면 n개의 Selector를 통해 2^n개의 입력 단자 중 하나를 선택하여 출력으로 내보내는 논리 회로

- 즉, 동시에 2^n개 입력 데이터가 들어오더라도 n개의 선택선에 의해 선택된 입력 단자만이 출력으로 전달된다.

- Q) MUX와 Encoder의 차이점은 무엇인가?

- Encoder에서 1) 2개 이상의 입력 단자에서 True일 수 없었으며, 2) 선택선이 없었고, 3) 진리표에 의해 정해진 입력이 들어오면 정해진 출력이 출력되었다.

- MUX에서는 1) 동시에 여러 입력이 들어올 수 있어 2개 이상의 입력 단자에서 True일 수 있으며, 2) 선택선에 의해 여러 개의 입력 단자 중 하나가 선택되었고, 3) 진리표와 상관 없이 선택선에 의해 결정되었다.

- Q) 왜 선택선은 n개를 갖는가?

A) 2^n 개의 입력 단자에서 하나를 선택한다는 것은 " 0 ~ 2^n-1개 중에서 하나를 선택한다." 라는 의미이며, 이는 선택선은 " 0 ~ 2^n-1을 표현할 수 있어야 한다."를 의미한다. 따라서 선택선이 0 ~ 2^n-1를 표현하기 위해서 n개의 선을 가져야 한다.

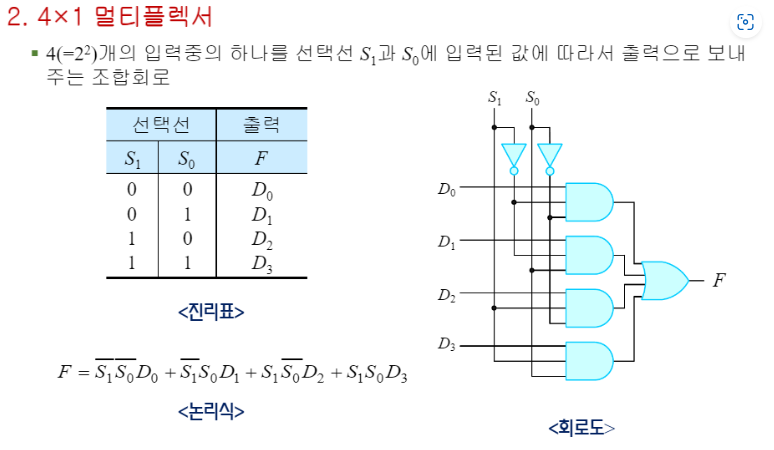

2. 4 X 1 MUX

- 4 X 1 MUX의 진리표와 게이트 회로는 다음과 같다.

- 2bit 로 구성된 Selector 값(S0, S1)에 따라 AND을 통과하는 입력 신호 D가 결정된다.

- ex) S1 = 1, S2 = 0 이면 동시에 D0, D1, D2, D3 입력 값이 들어온다고 하더라도 Selector와 AND 게이트에 의해 통과 되는 신호 값은 D2만 통과하고, 이를 OR 게이트를 통해 통합되어 하나의 출력으로 출력된다.

2.1. Dataflow modeling of 2 X 1 MUX (조건 연산자)

<Source code>

module MUX_2X1_Dataflow_modeling(

input [1:0] data ,

input selector,

output signal );

assign signal = (selector) ? data[1] : data[0];

endmodule

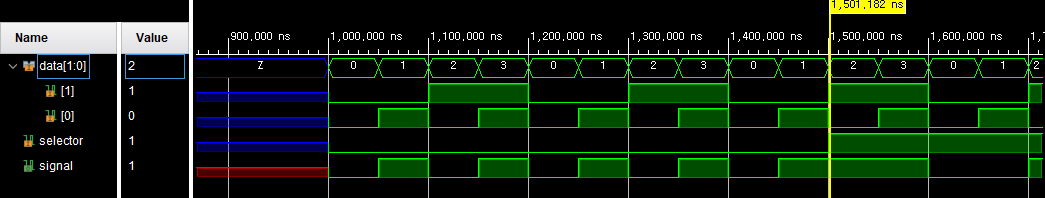

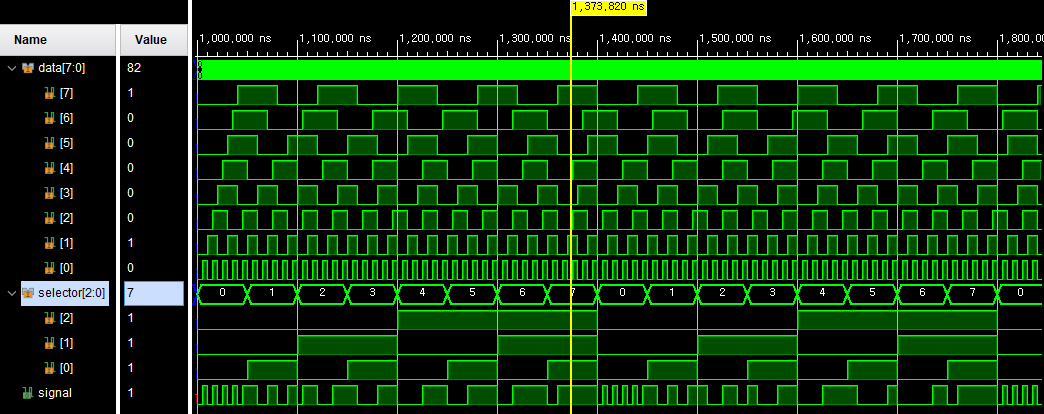

<Simulation>

<Analysis>

- 소스 코드를 분석하면 다음과 같다.

- 1bit의 선택선에 의해 두 개의 입력선 중 하나를 선택하여 출력을 내보낸다.

- 조건 연산자를 이용하여 Selector가 0이면 data[0], Selector가 1이면 data[1]를 출력으로 내보낸다. - 시뮬레이션를 분석하면 다음과 같다.

- selector가 0이면 data[0]이 출력값 (signal)에 그대로 나타난다.

- selector가 1이면 data[1]이 출력값 (signal)에 그대로 나타난다.

2.2. Dataflow modeling of 2 X 1 MUX (배열 인덱스)

<Source code>

module MUX_2X1_Dataflow_modeling(

input [1:0] data ,

input selector,

output signal );

// assign signal = (selector) ? data[1] : data[0];

assign signal = data[selector];

endmodule

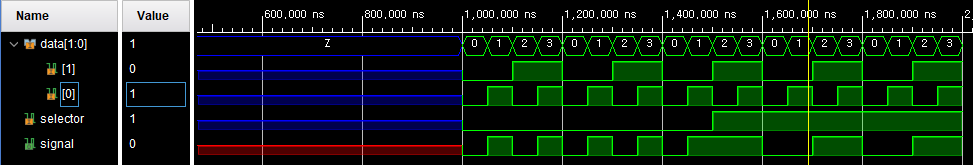

<Simulation>

<Analysis>

- 소스 코드를 분석하면 다음과 같다.

- 위 Dataflow modeling은 조건 연산자를 통해 구현했다면 이번에는 배열와 인덱스를 통해 구현하였다.

- data 배열은 입력 단자들의 값을 갖고 있는 배열로서 selector 값을 인덱스를 넣어줌으로서 selector를 통해 입력 단자들 중에서 하나를 선택하는 결과를 얻을 수 있다.

- 배열의 인덱스 값으로 10진수 뿐만 아니라 2진수 값을 넣어줌으로서 Random access가 가능하다. - 시뮬레이션를 분석하면 다음과 같다.

- 위 Dataflow modeling of 2 X 1 MUX (조건 연산자) 와 동일한 시뮬레이션 결과를 얻었다.

- selector가 0이면 data[0]이 출력값 (signal)에 그대로 나타난다.

- selector가 1이면 data[1]이 출력값 (signal)에 그대로 나타난다.

2.3. Dataflow modeling of 4X2 MUX

<Source code>

module MUX_4X2_Dataflow_Modeling(

input [3:0] data,

input [1:0] selector,

output signal );

// 4개 입력선들 가운데에서 Selector에 의헤

// 선택 받은 입력선을 출력한다.

assign signal = data[selector];

endmodule

<Simulation>

<Analysis>

- 소스 코드를 분석하면 다음과 같다.

- 입력 단자는 4개의 입력 단자로 구성되어 있으며, 이들 중 하나만이 선택선에 의해 선택되어 출력된다.

- 선택선은 4개의 입력 단자 중 하나를 선택해야 하기 때문에 2bit 크기를 가져야 한다.

- 이를 조건 연산자를 통해 표현하는 것은 배열, 인덱스를 통해 표현하는 것보다 상대적으로 복잡하기 때문에 배열, 인덱스 형태로 표현혔다.

- assign signal = data[selector] 는 "입력 단자를 원소를 갖는 배열에서 인덱스 값을 selector를 줌으로서 4개의 입력 단자 중 selector 번째 입력 단자의 값을 출력으로 출력한다." 는 의미이다. - 시뮬레이션을 분석하면 다음과 같다.

- Selector의 값에 따라 0 ~ 3번째 입력 단자 중 하나를 선택하여 해당하는 입력 단자의 출력 값을 출력으로 내보낸다.

- ex) Selector 값이 2인 경우, data[2], 즉, 2번째 입력 단자의 입력 값을 출력으로 내보낸다.

- 즉, 위와 같이 동시 입력 단자 4개에서 동시에 입력으로 들어와도 Selector에 의해 선택된 입력 단자만이 출력으로 나가게 된다.

2.4. Dataflow modeling of 8X1 MUX

<Source code>

module MUX_8X1_Dataflow_modeling(

input[7:0] data,

input[2:0] selector,

output signal );

assign signal = data[selector];

endmodule

<Simulation>

<Analysis>

- 소스 코드를 분석하면 다음과 같다.

- 8개의 입력선 중 3개의 선택선에 의해 1개를 선택하여 해당 입력선을 통해 들어오는 데이터를 출력으로 내보낸다.

- 따라서 8개의 입력선에서 동시에 여러 개의 데이터가 들어온다고 하더라도 출력으로 나가는 건 선택선에 의해 선택된 입력선의 데이터, 단 하나이다.

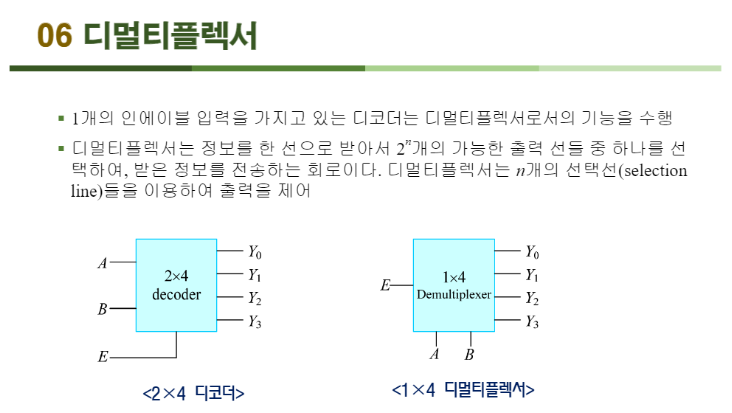

3. 디멀티플렉서 (DEMUX)

- MUX는 2^n개의 입력선과 n개의 선택선, 1개의 출력선으로 이루어져 있으며, 여러 개의 입력선 중 n개의 x선택선에 의해 선택된 입력선을 통해 들어오는 데이터를 출력으로 내보낸다.

- 반대로 DEMUX는 1개의 입력선과 n개의 선택선, 2^n개의 출력선으로 이루어져 있다.

- DEMUX는 1개의 입력선으로부터 들어온 데이터를 출력으로 내보내기 위해 2^n개의 출력선 중 하나를 선택해야 하는데, 이를 선택선이 선택하게 된다.

- n개의 선택선에 의해 선택된 출력선으로 입력선으로 부터 들어온 데이터를 출력으로 내보낸다.

3.1. Dataflow modeling of 1X4 DEMUX

<Source code>

module DEMUX_1X4_Dataflow_modeling(

input signal,

input [1:0] selector,

output [3:0] data);

assign data = (selector == 2'b00)? {3'b000, signal} :

(selector == 2'b01)? {2'b00, signal, 1'b0} :

(selector == 2'b10)? {1'b0, signal, 2'b00} :

(selector == 2'b11)? {signal, 3'b000} : 4'b0000 ;

endmodule

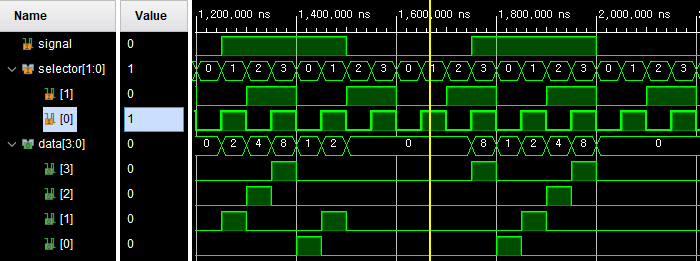

<Simulation>

<Analysis>

- 코드를 분석하면 다음과 같다.

- 하나의 입력선으로부터 데이터를 입력받는다.

- 출력선은 총 4개로 이루어져 있지만, 이중에서 실질적으로 들어온 데이터를 출력하는 선은 단 하나이다.

- 2개의 선택선에 의해 4개 중 하나를 선택하여 들어온 데이터를 출력선으로 사용한다.

- 이를 위해 조건 연산자를 사용하여 선택선의 값에 따라 하나의 출력선으로 출력이 발생하도록 설계했다.

- {} 는 여러 비트 또는 변수들을 하나로 묶는 데 사용한다.

Verilog에서 중괄호 ,{}를 "비트 결합 연산자"라고 한다.

ex, 예를 들어, {3'b110, 1'b0}은 3비트의 110과 1비트의 0을 하나의 4비트 벡터로 만든다. - 시뮬레이션을 분석하면 다음과 같다.

- 선택선의 값에 따라 그에 해당하는 출력선으로 입력 값이 출력됨을 확인할 수 있다.

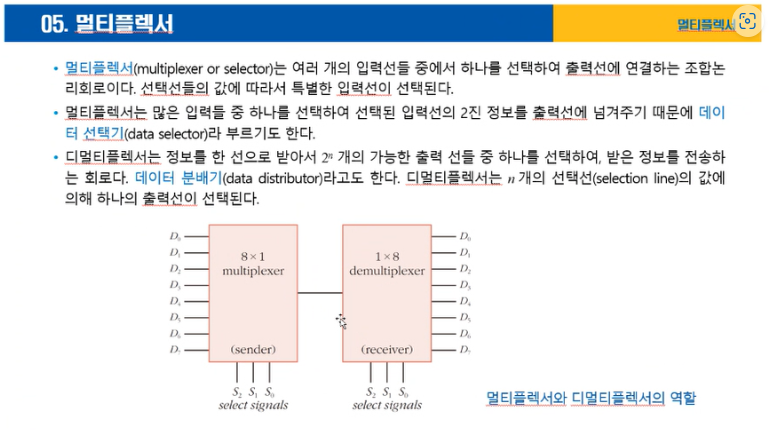

4. MUX와 DEMUX의 조합

- 이번에는 아래와 같이 MUX와 DEMUX를 조합해보겠다.

- 즉, MUX에서는 2^n개의 입력선 중 n개의 선택선에 의해 선택된 입력선으로 부터 들어오는 데이터를 출력으로 내보내겠다. 그리고, 이렇게 MUX측에서 출력으로 내보낸 데이터를 DEMUX측에서 받는다.

- MUX에서는 n개의 선택선에 의해 2^n개의 입력선 중 1개를 선택하여 입력으로 들어온 데이터를 해당 선택된 출력선으로 내보낸다.

- 이번 구현에서는 4X1 MUX와 1X4 DEMUX의 조합으로 구현해보겠다.

4.1. 4 X 1 MUX와 1 X 4 DEMUX의 조합

<Source code>

// Dataflow Modeling of MUX.

module MUX_4X1_Dataflow_Modeling (

input [3:0] data,

input [1:0] selector,

output signal );

assign signal = data[selector];

endmodule

// Dataflow Modeling of DEMUX

module DEMUX_1X4_Dataflow_Modeling (

input signal,

input [1:0] selector,

output [3:0] data);

assign data = (selector == 2'b00) ? {3'b000, signal} :

((selector == 2'b01) ? {2'b00, signal, 1'b0} :

((selector == 2'b10) ? {1'b0, signal, 2'b00} :

((selector == 2'b11) ? {signal, 3'b000} : 4'b0000)));

endmodule

// Structural Modeling of MUX and DEMUX

module MUX_4X1_DEMUX_1X4_Structural_Modeling(

input [3:0] input_signal,

input [1:0] selector_MUX, selector_DEMUX,

output [3:0] output_signal );

// MUX와 DEMUX를 연결하는 Wire

wire line;

MUX_4X1_Dataflow_Modeling MUX_0(.data(input_signal), .selector(selector_MUX), .signal(line));

DEMUX_1X4_Dataflow_Modeling DEMUX_0(.signal(line), .selector(selector_DEMUX), .data(output_signal));

endmodule

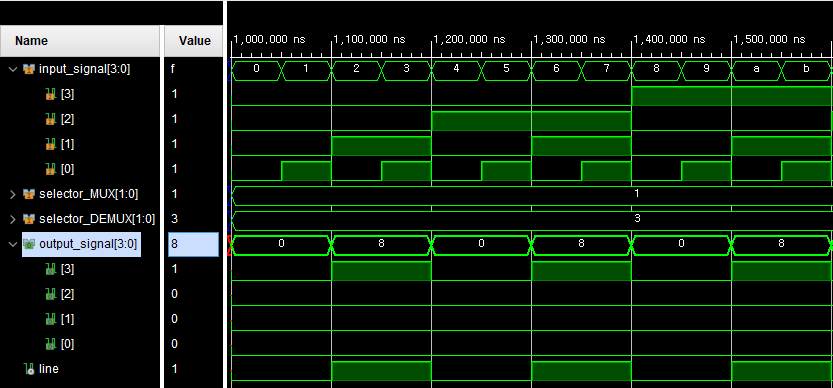

<Simulation>

<Analysis>

- 소스 코드를 분석하면 다음과 같다.

- MUX 측에서 4개의 입력선들 중에서 선택선에 의해 1개의 입력선을 선택한다.

- MUX 측에서 선택받은 입력선으로 들어오는 데이터를 MUX의 출력으로 내보낸다.

- DEMUX 측에서 MUX측으로부터 하나의 입력선을 통해 데이터를 입력받는다.

- DEMUX의 선택선을 통해 4개의 출력선들 중 하나를 선택하여 해당 데이터를 출력한다.

- DEMUX의 삼항 연산자에서 사용한 중괄호, {}는 "비트 결합 연산자"이다. - 시뮬레이션을 분석하면 다음과 같다.

- MUX, DEMUX의 선택선에 의해 선택된 입력선, 출력선은 서로 연결되어 데이터를 입/출력한다.

< Selector of MUX : 1, Selector of DEMUX : 3 >

- MUX측에서 1번째 입력선으로 부터 들어오는 데이터를 받아서 DEMUX측에서 3번째 출력선으로 내보낸다.

< Selector of MUX : 3, Selector of DEMUX : 0 >

- MUX측에서 3번째 입력선으로 부터 들어오는 데이터를 받아서 DEMUX측에서 0번째 출력선으로 내보낸다.

'RTL Design > Verilog RTL 설계' 카테고리의 다른 글

| Verilog RTL 설계 (6월 24일 - 4, 순차 논리 회로, Latch) (0) | 2024.06.26 |

|---|---|

| Verilog RTL 설계 (6월 24일 - 3) (0) | 2024.06.25 |

| Verilog RTL 설계 (6월 24일 - 1) (0) | 2024.06.24 |

| Verilog RTL 설계 (6월 13일 - 5) (1) | 2024.06.15 |

| Verilog RTL 설계 (6월 13일 - 4) (1) | 2024.06.15 |