Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| 30 |

Tags

- BASYS3

- atmega 128a

- vivado

- Pspice

- hc-sr04

- dataflow modeling

- LED

- Algorithm

- structural modeling

- pwm

- DHT11

- FND

- behavioral modeling

- gpio

- half adder

- D Flip Flop

- Edge Detector

- test bench

- Recursion

- prescaling

- ring counter

- java

- stop watch

- i2c 통신

- KEYPAD

- uart 통신

- ATMEGA128A

- verilog

- soc 설계

- Linked List

Archives

- Today

- Total

거북이처럼 천천히

Verilog RTL 설계(7월 16일 - 4, Basys3 FND 입문) 본문

1. Basys3의 FND 다 켜보기

- Basys3의 FND를 다 켜보도록 하겠다.

- 특별한 데이터를 FND를 통해 출력하지 않는다.

1.1. Basys3의 FND는 어떤 구조를 갖는가?

- Basys3의 FND의 회로도는 다음과 같은 구조를 갖는다.

- Basys3는 Common anode 구조로 설계되어 있다.

- 7-Segment를 구성하는 Diode들의 cathode들은 GND로 연결되어 있는 상태이다.

- 따라서 Diode들의 anode에 Vcc 값을 주게 되면 전위차에 의해 전류가 anode에서 cathode로 흐르게 되며, 이로인해 다이오드에 불이 들어오게 된다.

1.2. BJT는 어떻게 동작하는가?

- BJT의 전류의 방향을 나타내는 화살표가 emitter에서 Base로 향하고 있기 때문에 PNP형 BJT이다.

- 따라서 Base의 전압 레벨이 Low 레벨이면 Emiter에서 Collector 전류가 흐르게 된다.

- 따라서 anode 값이 0이면 switch가 ON되어 Emitter에서 Collector가 연결되고, 각각의 diode의 anode의 전압레벨이 High가 되기 때문에 전위차에 의해 다이오드에 전류가 흘러 다이오드에 불이 켜지게 된다.

- 반대로 anode 값이 1이면 Swith가 OFF되어 Emitter와 Collector가 연결되지 않아 각각의 diode의 cnode의 전압레벨이 Low가 되고, canode와 cathode의 전압 레벨이 모두 Low이기 때문에 다이오드에 전류가 흐르지 않고, 다이오드에 불이 켜지지 않는다.

< Source >

module Turn_On_FND(

input clk, resest_p,

output [7:0] seg_7,

output [3:0] com );

assign com = 4'b0000;

assign seg_7 = 0;

endmodule- com 변수에 0 값을 대입함으로서 4개의 FND들의 anode의 전압 레벨이 High가 되며, 이로 인해 모든 FND들은 켜질 수 있다.

- seg_7 변수에 1을 대입함으로서 7-segment를 구성하는 모든 다이오드에 불이 켜지게 된다.

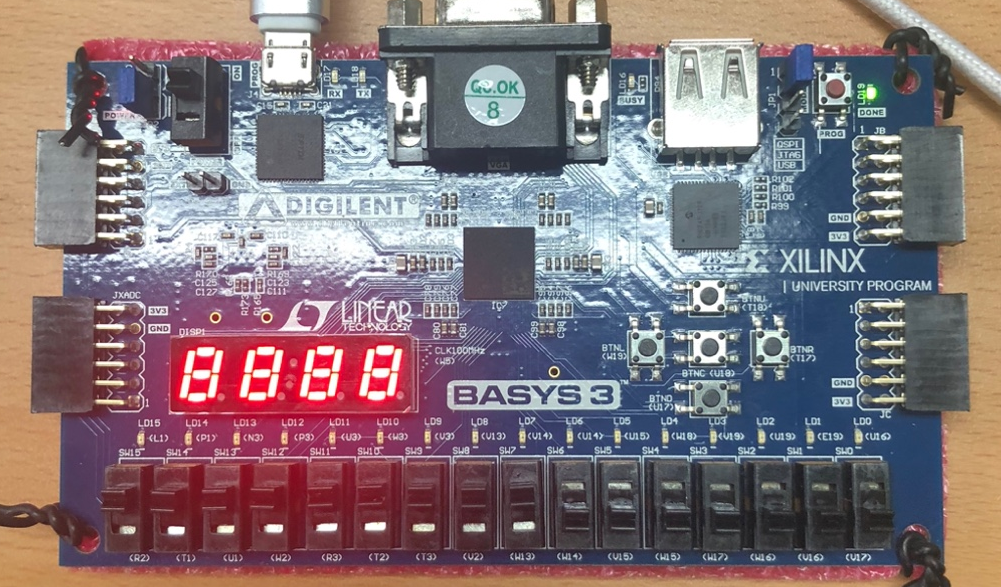

< Basys3 >

2. Switch를 통한 FND 제어

- 이번에는 간단하게 Switch을 통한 FND 제어를 하도록 하겠다.

- 0번 ~ 3번 Switch는 Common anode의 출력을 제어한다.

- 8번 ~ 15번은 각각의 다이오드의 Cathode의 출력을 제어한다.

2.1. Swith가 올라 갔을 때와 내려갔을 때의 전압 레벨은 각각 무엇인가?

- Switch를 올리면 해당 FND의 자리(com)의 값을 1로 인식한다.

- Switch를 내리면 해당 FND의 자리(com)의 값을 0로 인식한다.

< Source >

module Turn_On_FND_By_Using_Switch(

input clk, resest_p,

input [15:0] sw,

output [3:0] com,

output [7:0] seg_7 );

// Control com by using button 0 ~ 3

assign com = sw[3:0];

// Control 7-segment by using button 8 ~ 15

assign seg_7 = sw[15:8];

endmodule

< Basys3 >

'RTL Design > Verilog RTL 설계' 카테고리의 다른 글

| Verilog RTL 설계(7월 17일 - 1, FND Shifting) (0) | 2024.07.18 |

|---|---|

| Verilog RTL 설계(7월 16일 - 5, 16진수 값을 FND로 출력) (0) | 2024.07.18 |

| Verilog RTL 설계(7월 16일 - 3, Basys3 입문) (0) | 2024.07.18 |

| Verilog RTL 설계(7월 16일 - 2, Prescaler) (0) | 2024.07.17 |

| Verilog RTL 설계(7월 16일 - 2, SRAM) (0) | 2024.07.16 |