Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 |

Tags

- KEYPAD

- LED

- atmega 128a

- i2c 통신

- test bench

- hc-sr04

- verilog

- ring counter

- structural modeling

- Algorithm

- Recursion

- dataflow modeling

- ATMEGA128A

- D Flip Flop

- behavioral modeling

- pwm

- java

- half adder

- stop watch

- vivado

- uart 통신

- prescaling

- BASYS3

- Linked List

- Pspice

- DHT11

- FND

- soc 설계

- Edge Detector

- gpio

Archives

- Today

- Total

거북이처럼 천천히

Verilog RTL 설계(7월 12일 - 6, 링 카운터) 본문

1. Ring Counter

- Ring 형태로 순환되는 Counter

- 출력 값 중에서 하나의 비트 값만 1이고, 나머지 비트는 0을 갖게되며, 순차적으로 Shift되며 출력된다.

- Ring 형태로 순환되는 구조를 갖기 때문에 마지막 비트에서 다시 첫 번째 비트로 돌아 온다.

- n 개의 플립플롭을 갖는다면 n개의 서로 다른 상태를 갖는다.

- 주로 순차적인 흐름 및 제어 필요한 시스템에서 사용된다.

- Verilog는 병렬적 처리를 하기 때문에 순차적인 처리를 설계하고 싶을 경우, 링 카운터를 사용한다.

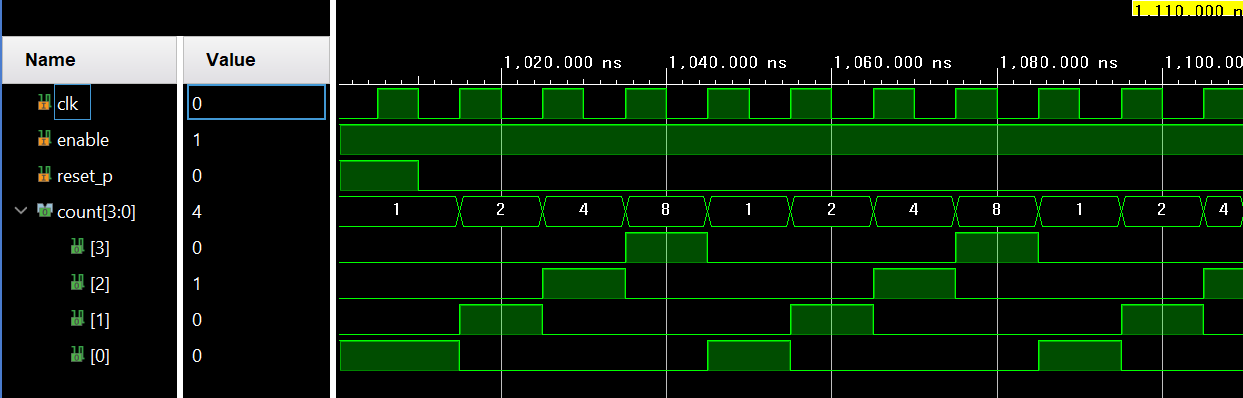

2. Behavioral modeling of Ring Counter (Positive edge trigger)

< Source >

// Behavioral Modeling of Ring Counter

module Behavioral_Modeling_Of_Ring_Counter_Positive(

input clk, enable, reset_p,

output reg [3:0] count );

always @(posedge clk or posedge reset_p) begin

if(reset_p) count = 4'b0001;

else if(enable) begin

case(count)

4'b0001 : count = 4'b0010;

4'b0010 : count = 4'b0100;

4'b0100 : count = 4'b1000;

4'b1000 : count = 4'b0001;

default : count = count;

endcase

end

end

endmodule

< Simulation >

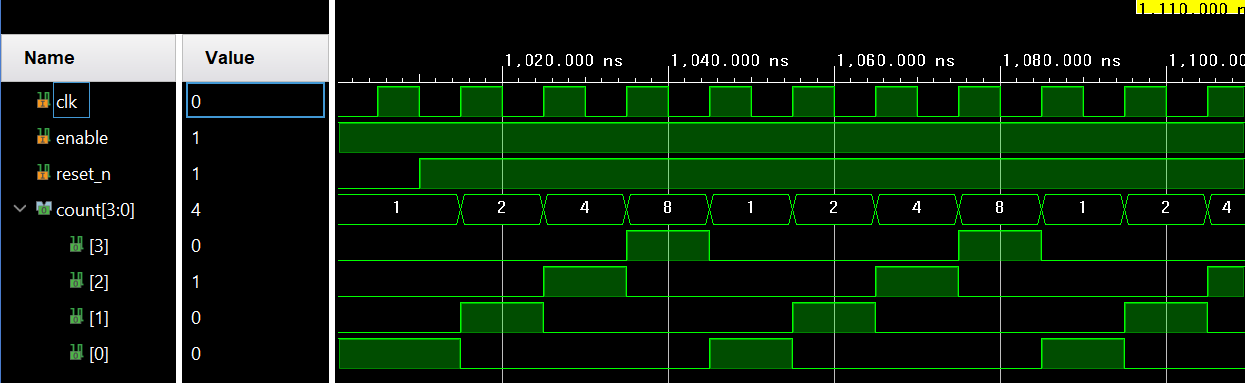

3. Behavioral modeling of Ring Counter by using shift operator (Negative edge trigger)

- Behavioral modeling of Ring Counter를 통해 알 수 있듯이 count 값이 왼쪽으로 1bit 씩 Shift 됨을 확인할 수 있다.

- 모든 입력 경우의 수에 대해서 출력을 정의할 필요 없이 Shift operator를 사용하여 구현할 수 있음을 생각할 수 있다.

< Source >

// Behavioral modeling of Ring Counter by using Shift operator

module Behavioral_Modeling_of_Ring_Counter_By_using_Shift_Operator(

input clk, enable, reset_n,

output reg [3:0] count );

always @(posedge clk or negedge reset_n) begin

if(!reset_n) count = 4'b0001;

else if(enable) begin

if(count == 4'b1000) count = 4'b0001;

else count = count << 1;

end

else count = count;

end

endmodule

< Simulation >

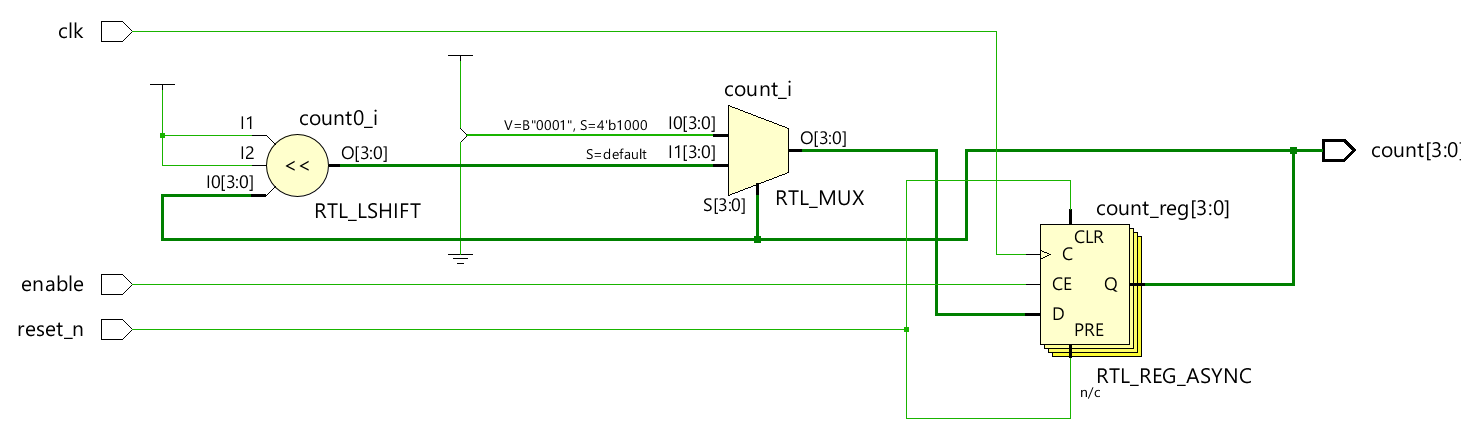

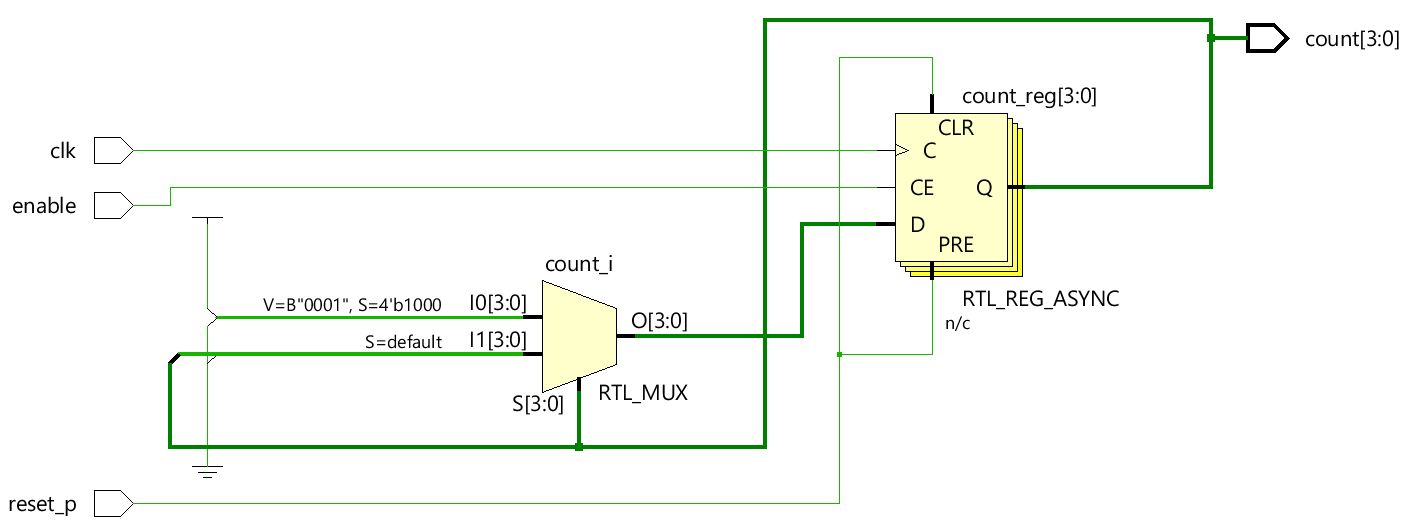

< RTL Analysis >

4. Behavioral Modeling of Ring Counter by using concatenation operator.

- Shift 연산자도 PDT (Propagation delay time)이 적기 때문에 충분히 좋은 코드이지만, 다음과 같이 결합 연산자로 Shift 연산자를 대신하면 Shift operator의 논리 회로가 필요없다.

- 즉, 결합 연산자를 통해 Shift 연산자를 대체할 수 있다.

- ★★★★★★

Q) 왜 Shift 연산자를 사용하지 않고, 왜 결합 연산자를 사용하는가?

A) RTL analysis 를 보게 되면 Shift 연산자를 수행하기 위한 회로가 생성되지 않았음을 확인할 수 있고, 이는 추가적으로 Shift 연산자를 위한 논리 회로를 생성하지 않음으로서 자원 절약을 할 수 있어 보다 효율적이라 볼 수 있다.

< Source >

// Behavioral modeling of ring counter by using concatenation operator.

module Behavioral_Modeling_of_Ring_Counter_By_using_concatenation_operator(

input clk, enable, reset_p,

output reg [3:0] count );

always @(posedge clk or posedge reset_p) begin

if(reset_p) count = 4'b0001;

else if(enable) begin

if(count == 4'b1000) count = 4'b0001;

else count = {count[2:0], 1'b0};

end

else count = count;

end

endmodule- count = {count[2:0], 1'b0}; : Shift 되어도 남아 있는 bit 자리수와 zero padding을 위한 0 값을 결합 연산자를 통해 결합함으로서 Shift 연산자와 유사한 기능을 수행할 수 있다.

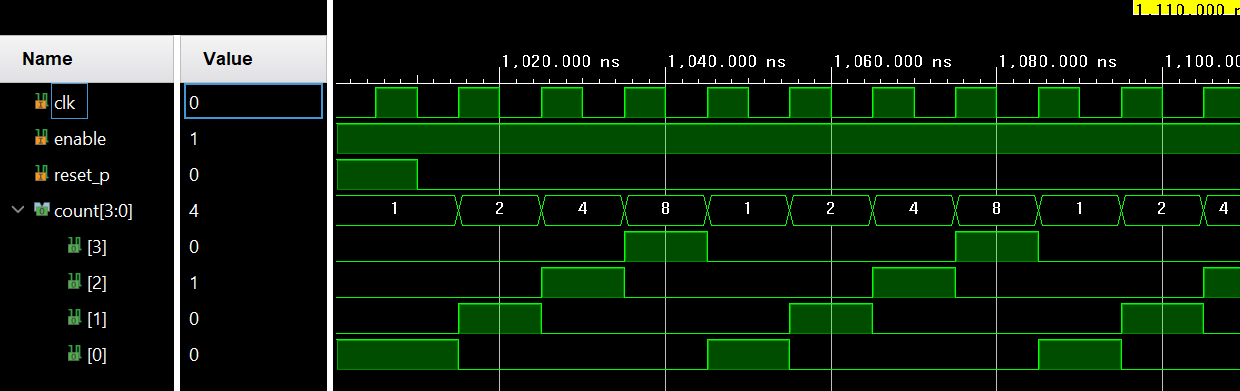

< Simulation >

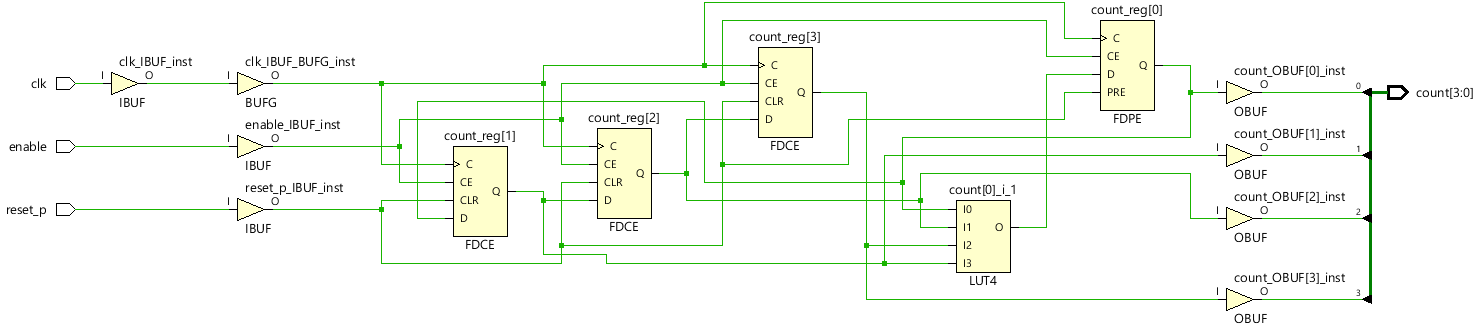

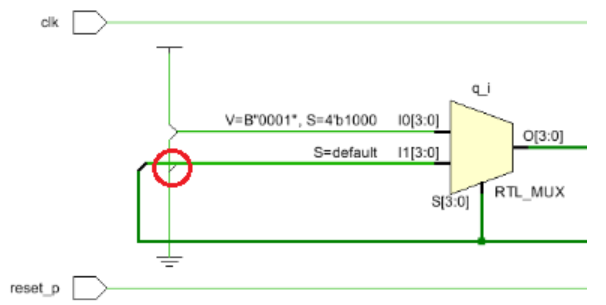

< RTL Analysis >

- Shift 연산자를 사용하지 않았기 때문에 Shift 연산자를 수행할 논리회로가 필요하지 않다.

- 따라서 결합 연산자로 이를 대체함으로서 자원의 절약을 할 수 있는 것이다.

< Synthesis >

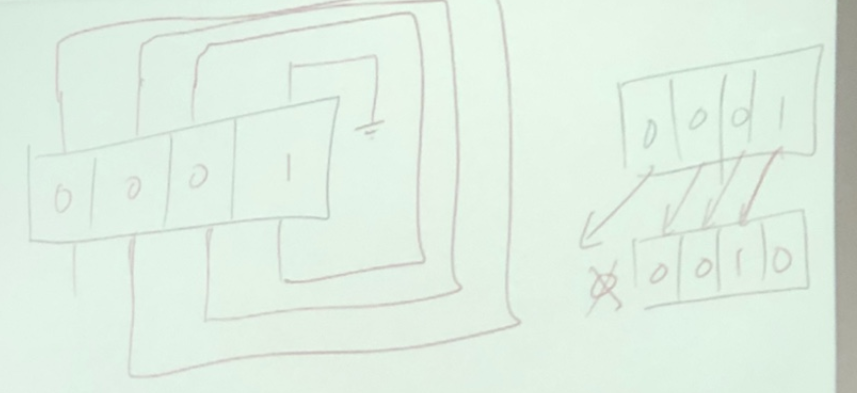

5. 왜 RTL analysis에서 아래 그림와 같이 GND에 연결하며, 이는 무엇을 의미하는가?

- count = {count[2:0], 1'b0} 코드를 보게 되면 결합 연산자를 이용하여 Shift 연산자를 대체하기 위해서 LSB에 Zero padding을 위해 1'b0 과 결합하였다.

- GND와 연결된 것도 Zero padding을 위해 접지와 연결된 것이다.

- 아래 그림을 보고, 생각하면 이해가 하기 상대적으로 쉬울 것이다.

'RTL Design > Verilog RTL 설계' 카테고리의 다른 글

| Verilog RTL 설계(7월 15일 - 1, 오전 내용 복습) (2) | 2024.07.15 |

|---|---|

| Verilog RTL 설계(7월 12일 - 6, Edge detector) (0) | 2024.07.15 |

| Verilog RTL 설계(7월 12일 - 5, 동기식 업/다운 카운터) (2) | 2024.07.14 |

| Verilog RTL 설계(7월 12일 - 4, 동기식 BCD 카운터) (2) | 2024.07.14 |

| Verilog RTL 설계(7월 12일 - 3, 동기식 카운터 - 2) (2) | 2024.07.14 |